#### About this Manual

We've added this manual to the Agilent website in an effort to help you support your product. This manual is the best copy we could find; it may be incomplete or contain dated information. If we find a more recent copy in the future, we will add it to the Agilent website.

#### **Support for Your Product**

Agilent no longer sells or supports this product. Our service centers may be able to perform calibration if no repair parts are needed, but no other support from Agilent is available. You will find any other available product information on the Agilent Test & Measurement website, <u>www.tm.agilent.com</u>.

#### HP References in this Manual

This manual may contain references to HP or Hewlett-Packard. Please note that Hewlett-Packard's former test and measurement, semiconductor products and chemical analysis businesses are now part of Agilent Technologies. We have made no changes to this manual copy. In other documentation, to reduce potential confusion, the only change to product numbers and names has been in the company name prefix: where a product number/name was HP XXXX the current name/number is now Agilent XXXX. For example, model number HP8648A is now model number Agilent 8648A.

## HP 64797 H8/3048 Emulator Terminal Interface

**User's Guide**

HP Part No. 64797-97000 January 1995

Edition 1

#### **Notice**

Hewlett-Packard makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

© Copyright 1995, Hewlett-Packard Company.

This document contains proprietary information, which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Hewlett-Packard Company. The information contained in this document is subject to change without notice.

HP is a trademark of Hewlett-Packard Company.

UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company Limited.

H8/3048<sup>™</sup> registered trademark of Hitachi Ltd.

Hewlett-Packard Company P.O. Box 2197 1900 Garden of the Gods Road Colorado Springs, CO 80901-2197, U.S.A.

**RESTRICTED RIGHTS LEGEND** Use, duplication, or disclosure by the U.S. Government is subject to restrictions set forth in subparagraph (C) (1) (ii) of the Rights in Technical Data and Computer Software Clause at DFARS 252.227-7013. Hewlett-Packard Company, 3000 Hanover Street, Palo Alto, CA 94304 U.S.A. Right for non-DOD U.S. Government Department and Agencies are as set forth in FAR 52.227-19(c)(1,2).

#### **Printing History**

New editions are complete revisions of the manual. The date on the title page changes only when a new edition is published.

A software code may be printed before the date; this indicates the version level of the software product at the time the manual was issued. Many product updates and fixes do not require manual changes, and manual corrections may be done without accompanying product changes. Therefore, do not expect a one-to-one correspondence between product updates and manual revisions.

Edition 1 64797-97000, January 1995

## **Using This Manual**

This manual is designed to give you an introduction to the HP 64797 H8/3048 Emulator. This manual will also help define how these emulators differ from other HP 64700 Emulators.

This manual will:

- give you an introduction to using the emulator

- explore various ways of applying the emulator to accomplish your tasks

- show you emulator commands which are specific to the H8/3048 emualtor

This manual will not:

tell you how to use each and every emulator/analyzer command (refer to the User's Reference manual)

## Organization

| Chapter 1  | An introduction to the H8/3048 emulator features and how they can help you in developing new hardware and software.                                     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2  | A brief introduction to using the H8/3048 Emulator. You will load and execute a short program, and make some measurements using the emulation analyzer. |

| Chapter 3  | How to plug the emulation probe into a target system.                                                                                                   |

| Chapter 4  | Configuring the emulator to adapt it to your specific measurement needs.                                                                                |

| Chapter 5  | How to use H8/3048 internal Flash ROM functions on the H8/3048 emulator.                                                                                |

| Appendix A | H8/3048 Emulator Specific Command Syntax and Error Message                                                                                              |

## Contents

#### 1 Introduction

2

| Purpose of the H8/3048 Emulator                  | . 1-1 |

|--------------------------------------------------|-------|

| Features of the H8/3048 Emulator                 | . 1-3 |

| Supported Microprocessors                        | . 1-3 |

| Clock Speeds                                     | . 1-4 |

| Emulation memory                                 | . 1-5 |

| Analysis                                         | . 1-5 |

| Registers                                        | . 1-5 |

| Breakpoints                                      | . 1-6 |

| Reset Support                                    | . 1-6 |

| Real Time Operation                              | . 1-6 |

| Easy Product Updates                             | . 1-6 |

| Limitations, Restrictions                        | . 1-7 |

| Foreground Monitor                               | . 1-7 |

| DMA Support                                      | . 1-7 |

| Watch Dog Timer in Background                    | . 1-7 |

| Monitor Break at Sleep/Standby Mode              |       |

| Hardware Standby Mode                            | . 1-7 |

| Interrupts in Background Cycles                  | . 1-7 |

| On-chip Flash Memory                             | . 1-7 |

| Evaluation chip                                  | . 1-7 |

| Getting Started                                  |       |

| Introduction                                     | . 2-1 |

| Before You Begin                                 | . 2-2 |

| A Look at the Sample Program                     | . 2-3 |

| Using the Help Facility                          | . 2-7 |

| Initialize the Emulator to a Known State         |       |

| Set Up the Proper Emulation Configuration        | . 2-9 |

| Set Up Emulation Conditions                      | . 2-9 |

| Mapping Memory                                   | 2-11  |

| Getting the Sample Program into Emulation Memory |       |

| Standalone Configuration                         |       |

| Transparent Configuration                        | 2-13  |

|                                                  |       |

**Contents-1**

| Remote Configuration                                | 2-15 |

|-----------------------------------------------------|------|

| For More Information                                |      |

| Looking at Your Code                                |      |

| Familiarize Yourself with the System Prompts        |      |

| Running the Sample Program                          | 2-18 |

| Stepping Through the Program                        |      |

| Tracing Program Execution                           | 2-20 |

| Predefined Trace Labels                             | 2-20 |

| Predefined Status Equates                           | 2-21 |

| Specifying a Trigger                                |      |

| Using Software Breakpoints                          | 2-25 |

| Displaying and Modifying the Break Conditions       | 2-25 |

| Defining a Software Breakpoint                      | 2-26 |

| Searching Memory for Strings or Numeric Expressions | 2-27 |

| Making Program Coverage Measurements                | 2-27 |

| Trace Analysis Considerations                       | 2-28 |

| How to Specify the Trigger Condition                | 2-28 |

| Store Condition and Disassembling                   | 2-30 |

| Triggering the Analyzer by Data                     | 2-32 |

|                                                     |      |

#### **3** In-Circuit Emulation

## 4 Configuring the H8/3048 Emulator

| Types of Emulator Configuration                 |  |  | 4-1 |

|-------------------------------------------------|--|--|-----|

| Emulation Processor to Emulator/Target System   |  |  | 4-1 |

| Commands Which Perform an Action or Measurement |  |  | 4-2 |

| Coordinated Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                        | -2                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

| System                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| Emulation Processor to Emulator/Target System 4                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

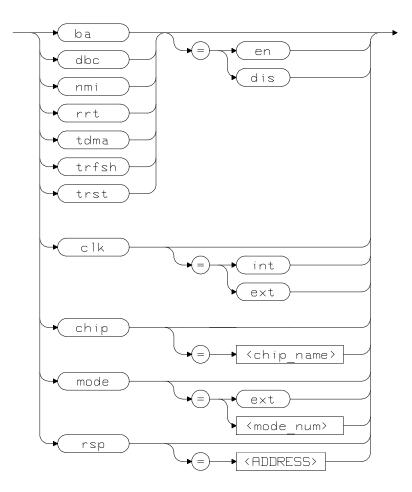

| cf                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -3                                                                               |

| cf ba                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -4                                                                               |

| cf chip                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -5                                                                               |

| cf clk                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -6                                                                               |

| cf dbc                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -7                                                                               |

| cf mode                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -8                                                                               |

| cf nmi                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -9                                                                               |

| cf rrt                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10                                                                               |

| cf rsp                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| cf tdma                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11                                                                               |

| cf trfsh                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12                                                                               |

| cf trst                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| Memory Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Break Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| Where to Find More Information                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| Using the On-chip Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -1                                                                               |

| Using the On-chip Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Using the On-chip Flash Memory Introduction                                                                                                                                                                                                                                                                                                                                                                                                                     | -1                                                                               |

| Using the On-chip Flash Memory Introduction                                                                                                                                                                                                                                                                                                                                                                                                                     | -1<br>-2                                                                         |

| Using the On-chip Flash Memory         Introduction                                                                                                                                                                                                                                                                                                                                                                                                             | -1<br>-2<br>-2                                                                   |

| Using the On-chip Flash Memory         Introduction       5         Memory Mapping       5         Flash Memory Registers       5         Programming/Erasing Flash Memory       5                                                                                                                                                                                                                                                                              | -1<br>-2<br>-2<br>-2                                                             |

| Using the On-chip Flash Memory         Introduction       5         Memory Mapping       5         Flash Memory Registers       5         Programming/Erasing Flash Memory       5         Programming Data       5                                                                                                                                                                                                                                             | -1<br>-2<br>-2<br>-2<br>-3                                                       |

| Using the On-chip Flash Memory         Introduction       5         Memory Mapping       5         Flash Memory Registers       5         Programming/Erasing Flash Memory       5         Programming Data       5         Erasing Data       5                                                                                                                                                                                                                | -1<br>-2<br>-2<br>-2<br>-3<br>-3                                                 |

| Using the On-chip Flash Memory         Introduction       5         Memory Mapping       5         Flash Memory Registers       5         Programming/Erasing Flash Memory       5         Programming Data       5         Erasing Data       5         Protectiom Mode       5         Boot Mode       5                                                                                                                                                      | -1<br>-2<br>-2<br>-2<br>-3<br>-3                                                 |

| Using the On-chip Flash Memory         Introduction       5         Memory Mapping       5         Flash Memory Registers       5         Programming/Erasing Flash Memory       5         Programming Data       5         Erasing Data       5         Protectiom Mode       5                                                                                                                                                                                | -1<br>-2<br>-2<br>-2<br>-3<br>-3                                                 |

| Using the On-chip Flash Memory         Introduction       5         Memory Mapping       5         Flash Memory Registers       5         Programming/Erasing Flash Memory       5         Programming Data       5         Erasing Data       5         Protectiom Mode       5         Boot Mode       5                                                                                                                                                      | -1<br>-2<br>-2<br>-3<br>-3<br>-4                                                 |

| Using the On-chip Flash Memory         Introduction       5         Memory Mapping       5         Flash Memory Registers       5         Programming/Erasing Flash Memory       5         Programming Data       5         Erasing Data       5         Protection Mode       5         Boot Mode       5         H8/3048 Emulator Specific Command Syntax                                                                                                     | -1<br>-2<br>-2<br>-3<br>-3<br>-4                                                 |

| Using the On-chip Flash Memory         Introduction       5         Memory Mapping       5         Flash Memory Registers       5         Programming/Erasing Flash Memory       5         Programming Data       5         Erasing Data       5         Protectiom Mode       5         Boot Mode       5         H8/3048 Emulator Specific Command Syntax         ACCESS_MODE       A                                                                         | -1<br>-2<br>-2<br>-3<br>-3<br>-3<br>-4                                           |

| Using the On-chip Flash Memory         Introduction       5         Memory Mapping       5         Flash Memory Registers       5         Programming/Erasing Flash Memory       5         Programming Data       5         Erasing Data       5         Protectiom Mode       5         Boot Mode       5         H8/3048 Emulator Specific Command Syntax         ACCESS_MODE       A         Summary       A                                                 | -1<br>-2<br>-2<br>-3<br>-3<br>-3<br>-4<br>-2<br>-2<br>-2<br>-2                   |

| Using the On-chip Flash Memory         Introduction       5         Memory Mapping       5         Flash Memory Registers       5         Programming/Erasing Flash Memory       5         Programming Data       5         Erasing Data       5         Protectiom Mode       5         Boot Mode       5         H8/3048 Emulator Specific Command Syntax       A         ACCESS_MODE       A         Syntax       A                                          | -1<br>-2<br>-2<br>-3<br>-3<br>-3<br>-4<br>-2<br>-2<br>-2<br>-2<br>-2<br>-2       |

| Using the On-chip Flash Memory         Introduction       5         Memory Mapping       5         Flash Memory Registers       5         Programming/Erasing Flash Memory       5         Programming Data       5         Erasing Data       5         Protectiom Mode       5         Boot Mode       5         H8/3048 Emulator Specific Command Syntax       A         ACCESS_MODE       A         Syntax       A         Defaults       A                 | -1<br>-2<br>-2<br>-3<br>-3<br>-3<br>-4<br>-2<br>-2<br>-2<br>-2<br>-2<br>-2<br>-2 |

| Using the On-chip Flash Memory         Introduction       5         Memory Mapping       5         Flash Memory Registers       5         Programming/Erasing Flash Memory       5         Programming Data       5         Erasing Data       5         Protectiom Mode       5         Boot Mode       5         H8/3048 Emulator Specific Command Syntax         ACCESS_MODE       A         Summary       A         Syntax       A         Defaults       A | -1<br>-2<br>-2<br>-3<br>-3<br>-3<br>-4<br>-2<br>-2<br>-2<br>-2<br>-2<br>-3<br>-3 |

5

Α

#### **Contents-3**

| Summary                          |

|----------------------------------|

| Syntax                           |

| Description                      |

| Examples                         |

| Related information              |

| DISPLAY_MODE                     |

| Summary                          |

| Syntax                           |

| Defaults                         |

| Related Information              |

| REGISTER CLASS and NAME          |

| Summary                          |

| Emulator Specific Error Messages |

| Message                          |

| Message                          |

| Message                          |

|                                  |

## Illustrations

| Figure 1-1. HP 64797 Emulator for the H8/3048 | <br> | 1-2   |

|-----------------------------------------------|------|-------|

| Figure 2-1. Sample Program Listing            | <br> | . 2-5 |

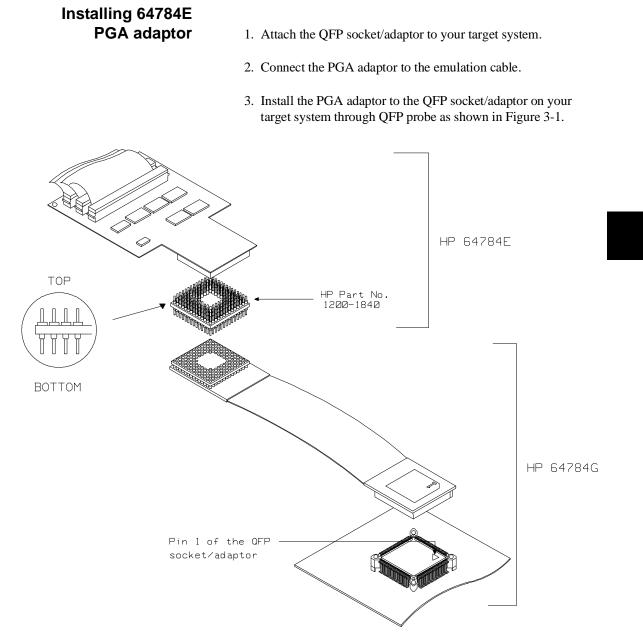

| Figure 3-1 Installing HP 64784E/HP 64784G     | <br> | 3-5   |

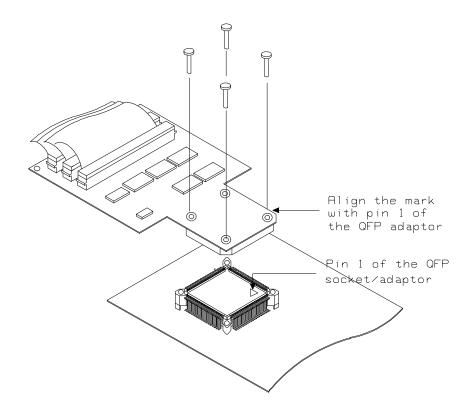

| Figure 3-2 Installing HP 64784D               | <br> | . 3-6 |

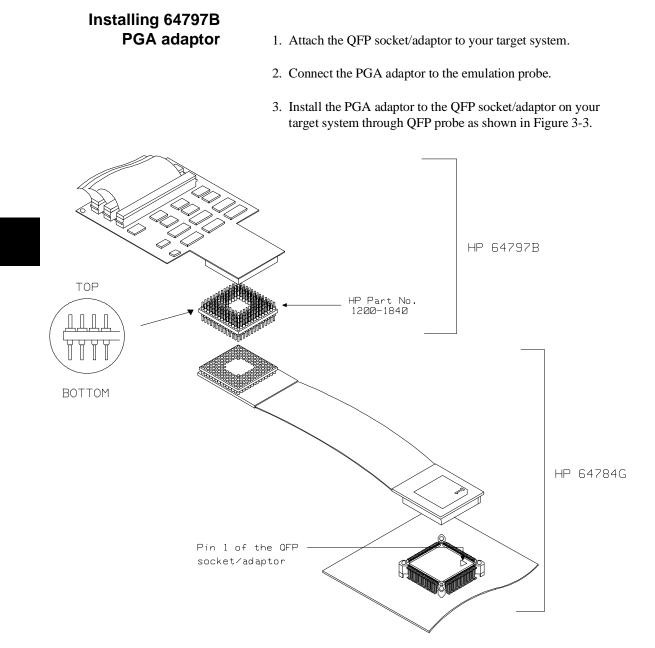

| Figure 3-3 Installing HP 64797B/HP 64784G     | <br> | 3-8   |

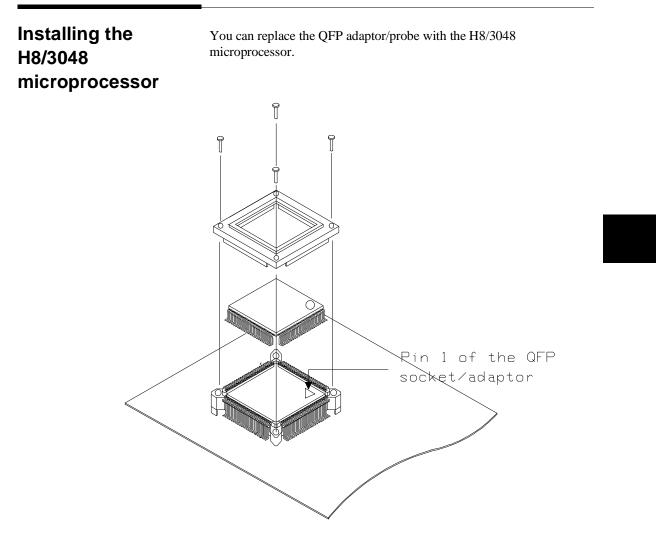

| Figure 3-4 Installing the H8/3048 processor   | <br> | 3-9   |

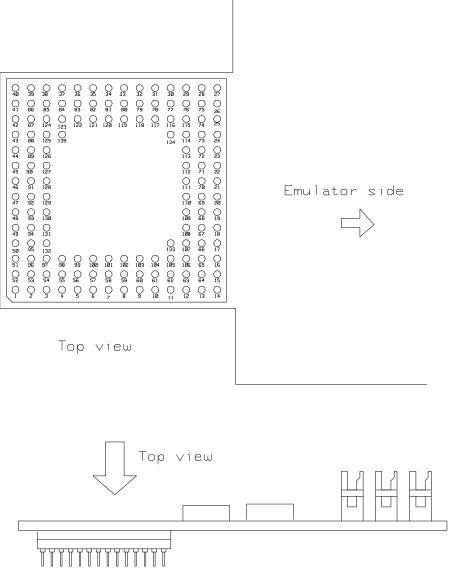

| Figure 3-5 PGA Adaptor Pin Assignment         | <br> | 3-15  |

## Tables

#### 4-Contents

| Table 3-5 Control signal timing (Vcc = $5.0V$ , f = $18MHz$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-20  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Table 3-6 Timing condition of On-chip supporting modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| (Vcc = 5.0V, f = 18MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-21  |

| Table 3-7 Bus timing (Vcc = $3.0V$ , f = $13MHz$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-23  |

| Table 3-8 Refresh controller timing (Vcc = $3.0V$ , f = $13MHz$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-25  |

| Table 3-9 Control signal timing (Vcc = $3.0V$ , f = $13MHz$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-26  |

| Table 3-10 Timing condition of On-chip supporting modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| (Vcc = 3.0V, f = 13MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-27  |

| Table 4-1 Clock Speeds         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | . 4-6 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

**Contents-5**

6-Contents

## Introduction

The topics in this chapter include:

- Purpose of the H8/3048 Emulator

- Features of the H8/3048 Emulator

# Purpose of the H8/3048 Emulator

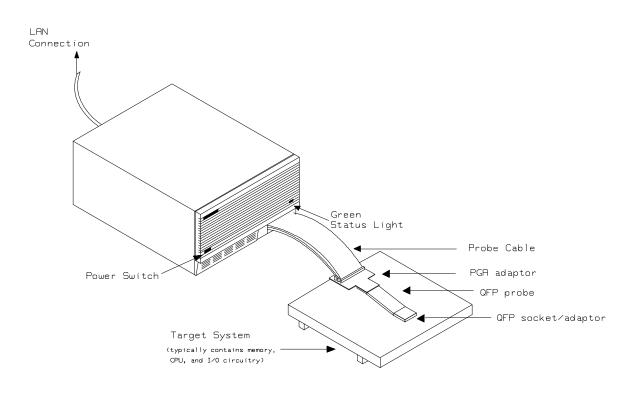

The H8/3048 Emulator is designed to replace the H8/3048 microprocessor in your target system so you can control operation of the microprocessor in your application hardware (usually referred to as the *target system*). The H8/3048 emulator performs just like the H8/3048 microprocessor, but is a device that allows you to control the H8/3048 microprocessor directly. These features allow you to easily debug software before any hardware is available, and ease the task of integrating hardware and software.

Introduction to the H8/3048 Emulator 1-1

1

Figure 1-1. HP 64797 Emulator for the H8/3048

1-2 Introduction to the H8/3048 Emulator

# Features of the H8/3048 Emulator

#### Supported Microprocessors

The HP 64797A H8/3048 emulator supports the microprocessors listed in Table 1-1.

| Supported Microprocessors |             |              |                |  |  |  |

|---------------------------|-------------|--------------|----------------|--|--|--|

| Туре                      | Package     | On-chip ROM  | Supply Voltage |  |  |  |

| H8/3048                   | 100 pin QFP | PROM         | 4.75 to 5.25V  |  |  |  |

|                           |             |              | 2.70 to 5.25V  |  |  |  |

|                           |             | Masked ROM   | 4.75 to 5.25V  |  |  |  |

|                           |             |              | 2.70 to 5.25V  |  |  |  |

| H8/3048F                  | 100 pin QFP | Flash Memory | 4.25 to 5.25V  |  |  |  |

|                           |             |              | 2.70 to 5.25V  |  |  |  |

| H8/3047                   | 100 pin QFP | Masked ROM   | 4.75 to 5.25V  |  |  |  |

|                           |             |              | 2.70 to 5.25V  |  |  |  |

| H8/3044                   | 100 pin QFP | Masked ROM   | 4.75 to 5.25V  |  |  |  |

|                           |             |              | 2.70 to 5.25V  |  |  |  |

#### Table 1-1. Supported Microprocessors

The H8/3048 emulator is provided without any adaptor and probe. To emulate each processor with your target system, you need to purchase appropriate adaptor and probe. To purchase them, contact your local HP sales representative.

The list of supported microprocessors in Table 1-1 is not necessarily complete. To determine if your microprocessor is supported or not, contact Hewlett-Packard.

#### Introduction to the H8/3048 Emulator 1-3

# **Clock Speeds** You can select whether the emulator will be clocked by the internal clock source or by the external clock source on your target system. You need to select a clock input conforming to the specification of Table 1-2.

Crystal ocsillator frequency of internal clock is 8MHz.

Refer to the "Configuration the Emulator" Chapter in this manual for more details.

| Emulation                  | Clock Speed                          |                                      |                                      |  |  |

|----------------------------|--------------------------------------|--------------------------------------|--------------------------------------|--|--|

| Memory                     | With HP64784D                        | With HP64784E                        | With HP64797B                        |  |  |

| 64726A<br>64727A<br>64728A | From 1 up to 16MHz<br>(System Clock) | From 1 up to 16MHz<br>(System Clock) | From 1 up to 13MHz<br>(System Clock) |  |  |

| 64729A                     | From 1 up to 18MHz<br>(System Clock) | From 1 up to 18MHz<br>(System Clock) | From 1 up to 13MHz<br>(System Clock) |  |  |

#### Table 1-2. Clock Speeds

#### 1-4 Introduction to the H8/3048 Emulator

#### Emulation memory

The H8/3048 emulator is used with one of the following Emulation Memory Cards.

- HP 64726A 128K byte Emulation Memory Card

- HP 64727A 512K byte Emulation Memory Card

- HP 64728A 1M byte Emulation Memory Card

- HP 64729A 2M byte Emulation Memory Card

When you use the HP64797A emulator over 16MHz, you have to use the HP 64729A 2M byte Emulation Memory Card.

You can define up to 16 memory ranges (at 512 byte boundaries and least 512 byte in length.) The emulator occupies 6K byte, which is used for monitor program and internal RAM of microprocessor mapped as emulation RAM, leaving 122K, 506K, 1018K, 2042K byte of emulation memory which you may use.

You can characterize memory range as emulation RAM (eram), emulation ROM (erom), target system RAM (tram), target system ROM (trom), or guarded memory (grd). The emulator generates an error message when accesses are made to guarded memory locations.

You can also configure the emulator so that writes to memory defined as ROM cause emulator execution to break out of target program execution.

**Analysis** The H8/3048 emulator is used with one of the following analyzers which allows you to trace code execution and processor activity.

- HP 64704A 80-channel Emulation Bus Analyzer

- HP 64703A 64-channel Emulation Bus Analyzer and 16-channel State/Timing Analyzer.

- HP 64794A/C/D Deep Emulation Bus Analyzer

The Emulation Bus Analyzer monitors the emulation processor using an internal analysis bus. The HP 64703A 64-channel Emulation Bus Analyzer and 16-channel State/Timing Analyzer allows you to probe up to 16 different lines in your target system.

**Registers** You can display or modify the H8/3048 internal register contents. This includes the ability to modify the program counter (PC) value so you can control where the emulator starts a program run.

#### Introduction to the H8/3048 Emulator 1-5

| Breakpoints             | You can set the emulator/analyzer interaction so the emulator will<br>break to the monitor program when the analyzer finds a specific state or<br>states, allowing you to perform post-mortem analysis of the program<br>execution. You can also set software breakpoints in your program.<br>This feature is realized by inserting a special instruction into user<br>program. One of undefined opcodes (5770 hex) is used as software<br>breakpoint instruction. Refer to the "Using Software Breakpoints"<br>section of "Getting Started" chapter for more information. |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset Support           | The emulator can be reset from the emulation system under your control; or your target system can reset the emulation processor.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Real Time Operation     | Real-time signifies continuous execution of your program at full rated<br>processor speed without interference from the emulator. (Such<br>interference occurs when the emulator needs to break to the monitor to<br>perform an action you requested, such as displaying target system<br>memory.) Emulator features performed in real time include: running<br>and analyzer tracing. Emulator features not performed in real time<br>include: display or modification of target system memory, load/dump<br>of target memory, display or modification of registers.       |

| Easy Product<br>Updates | Because the HP 64700 Series development tools(emulator, analyzer, LAN board) contain programmable parts, it is possible to reprogram the firmware and some of the hardware without disassembling the HP 64700B Card Cage. This means that you'll be able to update product firmware, if desired, without having to call to HP field representative to your site.                                                                                                                                                                                                           |

## Limitations, Restrictions

| Foreground Monitor                     | Foreground monitor is not supported for the H8/3048 emulator.                                                                                                                                                                                                   |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA Support                            | Direct memory access to the emulation by external DMAC is not allowed.                                                                                                                                                                                          |

| Watch Dog Timer in<br>Background       | Watch dog timer is suspended count up while the emulator is running in background monitor.                                                                                                                                                                      |

| Monitor Break at<br>Sleep/Standby Mode | When the emulator breaks into the background monitor, sleep or software standby mode is released. Then, PC indicates next address of "SLEEP" instruction.                                                                                                       |

| Hardware Standby<br>Mode               | Hardware standby mode is not supported for the H8/3048 emulator.<br>Hardware standby request from target system will drive the emulator<br>into the reset state.                                                                                                |

| Interrupts in<br>Background Cycles     | The H8/3048 emulator does not accept any interrupts while in background monitor. Such interrupts are suspended while running the background monitor, and will occur when context is changed to foreground.                                                      |

| On-chip Flash<br>Memory                | The H8/3048 emulator uses emulation memory instead of actual<br>on-chip flash memory. So, operation for on-chip flash memory is<br>different from H8/3048 microprocessor. Refer to "Using the On-chip<br>Flash Memory" chapter in this manual for more details. |

| Evaluation chip                        | Hewlett-Packard makes no warranty of the problem caused by the H8/3048 Evaluation chip in the emulator.                                                                                                                                                         |

Introduction to the H8/3048 Emulator 1-7

Notes

1-8 Introduction to the H8/3048 Emulator

## **Getting Started**

#### Introduction

This chapter will lead you through a basic, step by step tutorial designed to familiarize you with the use of the HP 64700 emulator for the H8/3048 microprocessor. When you have completed this chapter, you will be able to perform these tasks:

- Set up an emulation configuration for out of circuit emulation use

- Map memory

- Transfer a small program into emulation memory

- Use run/stop controls to control operation of your program

- Use memory manipulation features to alter the program's operation

- Use analyzer commands to view the real time execution of your program

- Use software breakpoint feature to stop program execution at specific address

- Search memory for strings or numeric expressions

- Make program coverage measurements

#### **Before You Begin**

Before beginning the tutorial presented in this chapter, you must have completed the following tasks:

- 1. Completed hardware installation of the HP 64700 emulator in the configuration you intend to use for your work:

- Standalone configuration

- Transparent configuration

- Remote configuration

- Local Area Network configuration

- 2. If you are using the Remote Configuration, you must have completed installation and configuration of a terminal emulator program which will allow your host to act as a terminal connected to the emulator. In addition, you must start the terminal emulator program before you can work the examples in this chapter.

- 3. If you have properly completed steps 1 and 2 above, you should be able to hit <RETURN> (or <ENTER> on some keyboards) and get one of the following command prompts on your terminal screen:

- U>

- R> M>

If you do not see one of these command prompts, retrace your steps through the hardware and software installation procedures outlined in the manuals above, verifying all connections and procedural steps. If you are still unable to get a command prompt, refer to the *HP 64700 Support Services Guide*. The guide gives basic trouble shooting procedures. If this fails, call the local HP sales and service office listed in the *Support Services Guide*.

In any case, you **must** have a command prompt on your terminal screen before proceeding with the tutorial.

### A Look at the Sample Program

The sample program "COMMAND\_READER" used in this chapter is shown figure 2-1. The program emulates a primitive command interpreter.

#### **Data Declarations**

Msg\_A, Msg\_B and Msg\_I are the messages used by the program to respond to various command inputs.

#### Initialization

The locations of stack and input area(Cmd\_Input) are moved into address registers for use by the program. Next, the CLEAR routine clears the command byte(the first location pointed to by Cmd\_Input - 0ff800 hex). Cmd\_Input contains 00 hex for late use.

#### Scan

This routine continuously reads the byte at location of Cmd\_Input until it is something other than a null character (00 hex); when this occurs, the Exe\_Cmd routine is executed.

#### Exe\_Cmd

Compares the input byte (now something other than a null) to the possible command bytes of "A" (ASCII 41 hex) and "B" (ASCII 42 hex), then jumps to the appropriate set up routine for the command message. If the input byte does not match either of these values, a branch to a set up routine for an error message is executed.

#### Cmd\_A, Cmd\_B, Cmd\_I

These routines set up the proper parameters for writing the output message: the number of bytes in the message is moved to the R3L register and the base address of the message in the data area is moved to address register ER4.

#### Write\_Msg

First the base address of the output area is copied to ER5. Then the Clear\_Old routine writes nulls to 32 bytes of the output area (this serves both to initialize the area and to clear old messages written during previous program passes).

Finally, the proper message is written to the output area by the Write\_Loop routine. When done, Write\_Loop jumps back to Clear and the command monitoring process begins again.

Using the various features of the emulator, we will show you how to load this program into emulation memory, execute it, monitor the program's operation with the analyzer, and simulate entry of different commands utilizing the memory access commands provided by the HP 64700 command set.

2-4 Getting Started

| 002000           |                                          | 1          |                                        | .SECTION                        | Table,DATA,LOCATE=H'2000                |

|------------------|------------------------------------------|------------|----------------------------------------|---------------------------------|-----------------------------------------|

| 002008           | 5448495320495320<br>4D45535341474520     | 2<br>3     | Msgs<br>Msg_A                          | .SDATA                          | "THIS IS MESSAGE A"                     |

| 002019           | 5448495320495320<br>4D45535341474520     | 4          | Msg_B                                  | .SDATA                          | "THIS IS MESSAGE B"                     |

|                  | 42<br>494E56414C494420<br>434F4D4D414E44 | 5          | Msg_I                                  | .SDATA                          | "INVALID COMMAND"                       |

| 002031           |                                          | 6<br>7     | End_Msgs                               |                                 |                                         |

| 001000           |                                          | 8          |                                        | .SECTION                        | Prog,CODE,LOCATE=H'1000                 |

|                  |                                          | 9          | ; * * * * * * * * * * * * * *          | * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

|                  |                                          | 10<br>11   | <pre>;* Set up the P</pre>             |                                 | * * * * * * * * * * * * * * * * * * * * |

| 001000           | 7A07000FF904                             | $11 \\ 12$ | ,                                      | MOV.L                           | #Stack, ER7                             |

|                  | 7A01000FF800                             | 13         |                                        | MOV.L                           | #Cmd Input, ER1                         |

|                  |                                          | 14         | ; * * * * * * * * * * * * * * *        | * * * * * * * * * * * * * * * * | *****                                   |

|                  |                                          | 15         | ;* Clear previo                        |                                 | * * * * * * * * * * * * * * * * * * * * |

| 00100C           | E900                                     | 16<br>17   | ;************************************* | MOV.B                           | #H'00,ROL                               |

|                  | 6AA8000FF800                             | 18         | Clear                                  | MOV.B<br>MOV.B                  | ROL,@Cmd Input                          |

| 001001           | 01110000110000                           | 19         | ; * * * * * * * * * * * * * *          |                                 | ****                                    |

|                  |                                          | 20         | ;* Read command                        | input byte. If                  | no command has been                     |

|                  |                                          | 21         |                                        | tinue to scan fo                |                                         |

| 001014           | 6A2A000FF800                             | 22<br>23   | 1                                      |                                 | *****                                   |

| 001014<br>00101A |                                          | 23<br>24   | Scan                                   | MOV.B<br>CMP.B                  | <pre>@Cmd_Input,R2L #H'00,R2L</pre>     |

| 00101C           |                                          | 25         |                                        | BEO                             | Scan                                    |

|                  |                                          | 26         | ; * * * * * * * * * * * * * *          | ***********                     | * * * * * * * * * * * * * * * * * * * * |

|                  |                                          | 27         |                                        | s been entered.                 |                                         |

|                  |                                          | 28<br>29   | ;* command A, c                        | ommand B, or inv                | alid command.<br>******                 |

| 00101E           | <b>۵۵41</b>                              | 29<br>30   | Exe Cmd                                | CMP.B                           | #H'41,R2L                               |

|                  | 5870000A                                 | 31         | HAC_CILL                               | BEO                             | Cmd A                                   |

| 001024           | AA42                                     | 32         |                                        | CMP.B                           | #H'42,R2L                               |

|                  | 58700010                                 | 33         |                                        | BEQ                             | Cmd_B                                   |

| 00102A           | 58000018                                 | 34<br>35   |                                        | BRA                             | Cmd_I<br>*****                          |

|                  |                                          | 35<br>36   | 1                                      |                                 | the number of bytes                     |

|                  |                                          | 37         |                                        | R4 = location                   | -                                       |

|                  |                                          | 38<br>39   | ;* Jump to the                         | routine which wr                | ites the message.                       |

| 00102E           | FB11                                     | 40         | Cmd_A                                  | MOV.B                           | #Msg_B-Msg_A,R3L                        |

|                  | 7A0400002000                             | 41         |                                        | MOV.L                           | #Msg_A,ER4                              |

| 001036           | 58000014                                 | 42<br>43   | • * * * * * * * * * * * * * * * *      | BRA                             | Write_Msg<br>******                     |

|                  |                                          | 43<br>44   | ;* Command B is                        |                                 |                                         |

|                  |                                          | 45         |                                        |                                 | * * * * * * * * * * * * * * * * * * * * |

| 00103A           | FB11                                     | 46         | Cmd_B                                  | MOV.B                           | #Msg_I-Msg_B,R3L                        |

| 001000           |                                          |            |                                        |                                 |                                         |

|                  | 7A0400002011<br>58000008                 | 47<br>48   |                                        | MOV.L<br>BRA                    | #Msg_B,ER4<br>Write_Msg                 |

Figure 2-1. Sample Program Listing

Getting Started 2-5

|                  |                      | 49<br>50 | ;* An invalid co                                                             | ommand is entered                   |                                         |

|------------------|----------------------|----------|------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------|

|                  |                      | 51       | ;**************************************                                      |                                     |                                         |

| 001046<br>001048 | FB0F<br>7A0400002022 | 52<br>53 | Cmd_I                                                                        | MOV.B<br>MOV.L                      | #End_Msgs-Msg_I,R3L<br>#Msg_I,ER4       |

|                  |                      | 54       | ,                                                                            |                                     | * * * * * * * * * * * * * * * * * * * * |

|                  |                      | 55       | ;* The destination area is cleared.<br>;************************************ |                                     |                                         |

|                  |                      | 56       | ,                                                                            |                                     |                                         |

|                  | 7A05000FF804         | 57       | Write_Msg                                                                    | MOV.L                               | #Msg_Dest,ER5                           |

| 001054           |                      | 58       | Clear_Old                                                                    | MOV.B                               | #H'20,R6L                               |

| 001056           |                      | 59       | Clear_Loop                                                                   | MOV.B                               | ROL,@ER5                                |

| 001058           |                      | 60       |                                                                              | ADDS.L                              | #1,ER5                                  |

| 00105A           |                      | 61       |                                                                              | DEC.B                               | R6L                                     |

| 00105C           | 46F8                 | 62       |                                                                              | BNE                                 | Clear_Loop                              |

|                  |                      | 63       |                                                                              |                                     | * * * * * * * * * * * * * * * * * * * * |

|                  |                      | 64       |                                                                              | ritten to the dea                   |                                         |

|                  |                      | 65       | ; * * * * * * * * * * * * * * *                                              | * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

|                  | 7A05000FF804         | 66       |                                                                              | MOV.L                               | #Msg_Dest,ER5                           |

| 001064           |                      | 67       | Write_Loop                                                                   | MOV.B                               | @ER4+,R6L                               |

| 001066           |                      | 68       |                                                                              | MOV.B                               | R6L,@ER5                                |

| 001068           |                      | 69       |                                                                              | ADDS.L                              | #1,ER5                                  |

| 00106A           |                      | 70       |                                                                              | DEC.B                               | R3L                                     |

| 00106C           | 46F6                 | 71       |                                                                              | BNE                                 | Write_Loop<br>*******                   |

|                  |                      | 72       |                                                                              |                                     |                                         |

|                  |                      | 73       | ;* Go back and scan for next command.                                        |                                     |                                         |

|                  |                      | 74       | ; * * * * * * * * * * * * * * *                                              | * * * * * * * * * * * * * * * * *   | * * * * * * * * * * * * * * * * * * * * |

| 00106E           | 409C                 | 75       |                                                                              | BRA                                 | Clear                                   |

|                  |                      | 76       |                                                                              |                                     |                                         |

| 0FF800           |                      | 77       |                                                                              | .SECTION                            | Data,DATA,LOCATE=H'FF800                |

|                  |                      | 78       | ;**********                                                                  | * * * * * * * * * * * * * * * * *   | * * * * * * * * * * * * * * * * * * * * |

|                  |                      | 79       | ;* Command input                                                             | t area.                             |                                         |

|                  |                      | 80       | ;***********                                                                 | * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| 0FF800           | 0000004              | 81       | Cmd_Input                                                                    | .RES.L                              | 1                                       |

|                  |                      | 82       | ;**********                                                                  | * * * * * * * * * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

|                  |                      | 83<br>84 |                                                                              | of the command me                   | essages.<br>********                    |

| 0FF804           | 00000100             | 85       | Msg_Dest                                                                     | .RES.W                              | н′80                                    |

| 0FF904           |                      | 86       | Stack                                                                        |                                     |                                         |

|                  | 00001000             | 87       |                                                                              | .END                                | Init                                    |

|                  |                      |          |                                                                              |                                     |                                         |

Figure 2-1. Sample Program Listing (Cont'd)

2-6 Getting Started

## Using the Help Facility

If you need a quick reference to the Terminal Interface syntax, you can use the built-in **help** facilities. For example, to display the top level **help** menu, type:

#### R>**help**

| help - display help i                                                         | information                                                                                                                                                          |

|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| help <group><br/>help -s <group><br/>help <command/><br/>help</group></group> | <ul> <li>print help for desired group</li> <li>print short help for desired group</li> <li>print help for desired command</li> <li>print this help screen</li> </ul> |

| VALID <group> NAME<br/>gram - system gr<br/>proc - processor</group>          |                                                                                                                                                                      |

|                                                                               | n commands<br>L commands (hp internal use only)<br>trace commands                                                                                                    |

You can type the **?** symbol instead of typing **help**. For example, if you want a list of commands in the **emul** command group, type:

#### R> ? emul

emul - emulation commands

|                                                         | -                                                      |                                           |

|---------------------------------------------------------|--------------------------------------------------------|-------------------------------------------|

| bbreak to monitor<br>bcbreak condition<br>bpbreakpoints | cpcopy memory<br>dumpdump memory<br>esemulation status | momodes<br>rrun user code<br>regregisters |

| cfconfiguration                                         | ioinput/output                                         | rstreset                                  |